# Using the CompactFlash(CF) Interface as an External Data Bus

### Applications

- High-volume data transfer (Ethernet, digital camera, multiple UARTs, parallel port, etc.)

- Supervisory and management (with low-latency response)

- Soft real-time control

#### Hardware

- CF bus has 11-bit, 3x2048kiB address space (PCMCIA uses a 26-bit, 64MiB address space)

- Three addressable regions: I/O, Memory and Attribute

- Bits in StrongARM MECR register set access timing for each region

## **Bus Signals**

| Bus Power<br>(CardBVcc)<br>PWR_EN<br>/CD[2:1]<br>/MEMRD,   | Voltage used to power bus<br>signals.<br>Power Enable GPIOs<br>Card Detects. To power the<br>bus signals, detect pins (/CDn)<br>must be pulled low.<br>Memory read/write or                                                                                                                                                                                   | Bitsy<br>Bitsy Plus<br>BitsyX | 15<br>23<br>00<br>00<br>2,49<br>21,35<br>6<br>25<br>0<br>25                 | 3.3 V<br>Bus Power<br>//CD[2:1]<br>//SI2:11 |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|

| /MEMWR                                                     | Attribute space read                                                                                                                                                                                                                                                                                                                                          |                               | 1                                                                           | GND                                         |

| /REG<br>/CE[2:1]                                           | 0=Attribute space, 1=Memory<br>space<br>Indicate the memory space<br>data transfer type (8-, 16-bit<br>data)                                                                                                                                                                                                                                                  | J9 CF<br>interface            | 19<br>27<br>0 9<br>0 9<br>4                                                 | /IPO (Ready)                                |

| /IORD, WR<br>/IOis16<br>/IRQ<br>/WAIT<br>/STSCHG<br>/RESET | I/O space read/write<br>0=I/O data is 16-bit, 1=8-bit<br>Interrupt Request to processor<br>CPU waits for this signal to go<br>high before completing a CF<br>bus operation. Use carefully,<br>as ALL CPU activity stops<br>while this line is low. PCCR<br>register can disable this signal.<br>Status Change interrupt<br>GPIO to reset device, if<br>needed |                               | 31<br>o<br>B<br>o<br>J<br>o<br>J<br>o<br>J<br>33<br>34<br>13<br>37,38<br>17 | /CE[2:1]                                    |

| Address Space   | CF: "Socket 1"           | PCMCIA: "Socket 0"       |

|-----------------|--------------------------|--------------------------|

| I/O space       | 0x3000 0000 to 3000 07ff | 0x2000 0000 to 23ff ffff |

| Attribute space | 0x3800 0000 to 3800 07ff | 0x2800 0000 to 2bff ffff |

| Memory space    | 0x3C00 0000 to 3c00 07ff | 0x2C00 0000 to 2fff ffff |

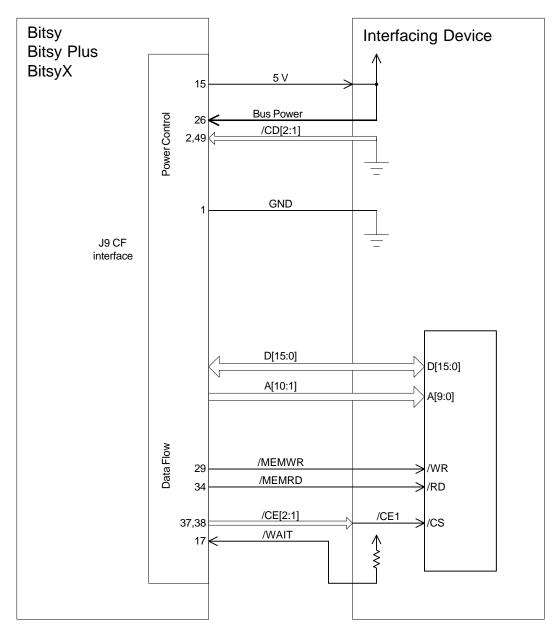

## Sample Application

The following example maps a 5V, 16-bit device to the memory space of the CF bus. Unused bus signals have been removed for clarity.

Notes:

- The CPU sets /CE[2:1] to logic 1 and 0, respectively, during 16-bit access. This design assumes that software always performs 16-bit writes. Decoding logic can be added, if desired.

- CF bus A1 maps to device's A0, since CF addresses are for 8-bit data.

- This design is not set up for power management. The device in this example will draw power from the ADS system even when the system is in Sleep mode

## O/S, General Issues

- Disable compact flash driver to avoid confusion or resource contention

- Screen may flicker if device uses long and/or slow memory cycles

### Windows CE

- Requires Platform Builder to create device driver, as there are a lot of header and LIB files needed that aren't included with SDK or even BSP.

- For applications that can tolerate latency, or are polled, could create a driver that maps to CF. System issues a Windows event when an interrupt occurs.

- DDTK includes an interrupt latency tester (uses system timer)

- CAN driver could be used as model for how to create and load an external device driver

#### Linux

- Map device driver to CF region of memory

- Map interrupt handler to S1ReadynInt

- Disable CF driver

#### References

- <u>Bitsy Plus Users Manual</u>. Applied Data Systems, 2002.

- Fiasal. <u>Inside PCCard: CardBus and PCMCIA Design (EDN Series for Design Engineers)</u>, Butterworth-Heineman. 1996

- Intel. <u>SA1110 Reference Manual</u>, *Section 10.7: PCMCIA*. (Order Number: 278240-004). October 2001. pp. 169-177

- Intel. SA1111 Developer's Manual, Chapter 12: PCMCIA (Intel Order No: 278242-003). July 2000.

- Mori and Welder. PCMCIA Developers Guide

#### **Document Revision History**

| REV | DESCRIPTION                                                                                                                                          | DATE      | BY |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----|

| 1   | Preliminary document                                                                                                                                 | 9/18/2001 | ak |

| 2   | Initial release<br>Add signal descriptions, updated block diagram,<br>references and application example                                             | 3/14/2003 | ak |

| 3   | Correct /IOis16 signal polarity and values<br>Add Socket 0/PCMCIA addresses<br>List full address range of CF and PCMCIA<br>Add this revision history | 3/18/2003 | ak |

|     | Add note about Wait signal<br>Indicate that StsChg can be used as an interrupt                                                                       | 4/8/2003  | ak |

|     |                                                                                                                                                      |           |    |