# **USER MANUAL**

# ZEUS PXA270 RISC based EPIC Single Board Computer

Rev. 5.0 - April 2009 - ETH\_ZEUS\_USM

#### **Disclaimer**

The information in this document is subject to change without notice and should not be construed as a commitment by any Eurotech company. While reasonable precautions have been taken, Eurotech assumes no responsibility for any error that may appear in this document.

#### Warranty

This product is supplied with a 3 year limited warranty. The product warranty covers failure of any Eurotech manufactured product caused by manufacturing defects. The warranty on all third party manufactured products utilised by Eurotech is limited to 1 year. Eurotech will make all reasonable effort to repair the product or replace it with an identical variant. Eurotech reserves the right to replace the returned product with an alternative variant or an equivalent fit, form and functional product. Delivery charges will apply to all returned products. Please check <a href="https://www.eurotech.com">www.eurotech.com</a> for information about Product Return Forms.

#### **Trademarks**

ARM and StrongARM are registered trademarks of ARM Ltd.

Intel and XScale are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

CompactFlash is the registered trademark of SanDisk Corp.

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

ZigBee is a registered trademark of the ZigBee Alliance.

All other trademarks recognised..

#### **Revision history**

| Issue no. | PCB        | Date                           | Comments                                            |

|-----------|------------|--------------------------------|-----------------------------------------------------|

| Α         | V1 Issue 2 | 8 <sup>th</sup> July 2006      | First full release of Manual for ZEUS.              |

| В         | V1 Issue 3 | 14 <sup>th</sup> November 2006 | Updated to reflect PCB changes, plus other updates. |

| С         | V1 Issue 4 | 25 <sup>th</sup> April 2007    | Updated to reflect PCB changes.                     |

| D         | V1 Issue 5 | 1 <sup>st</sup> October 2007   | Minor text corrections, Eurotech rebranding.        |

| E         | V1 Issue 5 | 17 <sup>th</sup> April 2009    | Minor updates and new branding.                     |

© 2009 Eurotech. All rights reserved.

For contact details, see page <u>125</u>.

# Contents

| Introduction                                  | 5  |

|-----------------------------------------------|----|

| ZEUS 'at a glance'                            | 7  |

| ZEUS features                                 | 9  |

| ZEUS support products                         | 12 |

| Product handling and environmental compliance | 13 |

| Conventions                                   | 14 |

| Getting started                               | 15 |

| Using the ZEUS                                | 15 |

| Detailed hardware description                 | 17 |

| ZEUS block diagram                            | 17 |

| ZEUS address map                              | 18 |

| PXA270 processor                              |    |

| PXA270 GPIO pin assignments                   |    |

| Interrupt assignments                         |    |

| On-Board GPIO expanders pin assignments       |    |

| Real time clock                               |    |

| Watchdog timer                                |    |

| Memory                                        |    |

| Wireless support                              |    |

| Expansion interfaces                          |    |

| SDIO                                          |    |

| CompactFlash                                  |    |

| PC/104 interface                              |    |

| Flat panel display                            |    |

| Audio                                         |    |

| Touchscreen controller                        |    |

| USB                                           |    |

| Ethernet                                      |    |

| Serial COM ports                              |    |

| CAN bus                                       |    |

| I <sup>2</sup> C bus                          |    |

| Quick Capture camera interface                |    |

| External General purpose I/O                  |    |

| Temperature sensor                            |    |

| JTAG and debug access                         |    |

| Power and power management                    |    |

| Processor payor management                    |    |

| Processor power management                    |    |

| Peripheral devices power management           |    |

| Connectors, LEDs and jumpers                  |    |

| Connectors                                    |    |

| Jumpers                                       |    |

| Status LEDs                                   |    |

| Appendix A - Specification                    |    |

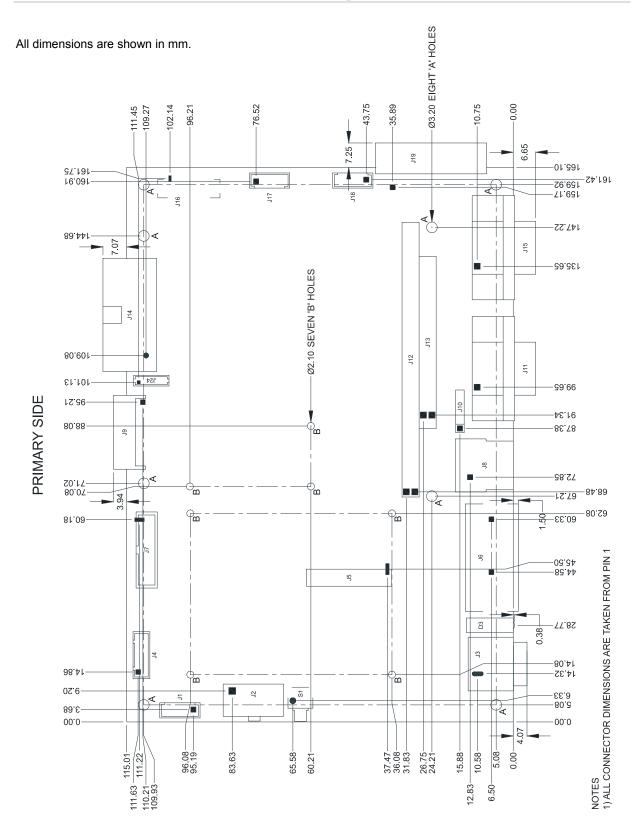

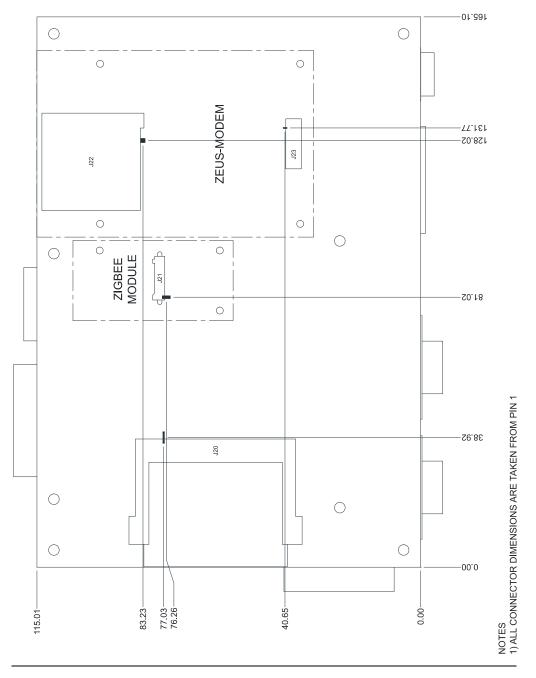

| Appendix B - Mechanical diagram               | 92 |

| Appendix C - Reference information                          | 94  |

|-------------------------------------------------------------|-----|

| Appendix D - Wireless modem datasheets                      | 96  |

| Appendix E - ZEUS Modem details                             | 110 |

| Appendix F - ZEUS-FPIF details                              | 114 |

| Appendix G - ZEUS-FPIF-CRT details                          | 119 |

| Appendix H - Acronyms and abbreviations                     | 122 |

| Appendix I - RoHS-6 Compliance - Materials Declaration Form | 124 |

| Furotech Group Worldwide Presence                           | 125 |

# Introduction

The ZEUS is an ultra-low power, high performance, single board computer based on the PXA270 processor. The PXA270 is an implementation of the Intel XScale micro architecture, combined with a comprehensive set of integrated peripherals including:

- · Flat panel graphics controller.

- Interrupt controller.

- Real time clock.

- Various serial interfaces.

The ZEUS board is based on the EPIC form factor. Included as standard are:

- Two Ethernet ports.

- Two USB host ports.

- Seven serial ports.

The ZEUS includes a site for a variety of wireless modems and a GPS receiver, and is designed to create cost effective solutions in asset monitoring, asset tracking, mobile terminals and network communication controllers. The ZEUS also includes an onboard vehicle compatible DC/DC power supply to simplify system integration.

The board is available in the standard variants specified in the following table:

| Variant              | Details                                                                  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------|--|--|--|--|

| ZEUS-M128-F32-001-R6 | Main features (all other features are included unless otherwise stated): |  |  |  |  |

|                      | <ul> <li>Onboard DC/DC PSU.</li> </ul>                                   |  |  |  |  |

|                      | Dual Ethernet ports.                                                     |  |  |  |  |

|                      | LVDS transmitter.                                                        |  |  |  |  |

|                      | CAN bus controller.                                                      |  |  |  |  |

|                      | 520MHz processor.                                                        |  |  |  |  |

|                      | This variant is included in the Development Kits.                        |  |  |  |  |

| ZEUS-M128-F32-002-R6 | Main features (all other features are included unless otherwise stated): |  |  |  |  |

|                      | Dual Ethernet ports.                                                     |  |  |  |  |

|                      | LVDS transmitter.                                                        |  |  |  |  |

|                      | CAN bus controller.                                                      |  |  |  |  |

|                      | <ul> <li>5V only (No DC/DC PSU).</li> </ul>                              |  |  |  |  |

|                      | <ul> <li>520MHz processor.</li> </ul>                                    |  |  |  |  |

|                      | continued                                                                |  |  |  |  |

| Variant                             | Details                                                                                      |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| ZEUS-M64-F32-003-R6                 | Main features (all other features are included unless otherwise stated):                     |  |  |  |

|                                     | <ul> <li>5V only (No DC/DC PSU).</li> </ul>                                                  |  |  |  |

|                                     | <ul> <li>No CAN bus, LVDS or secondary Ethernet port.</li> </ul>                             |  |  |  |

|                                     | • 520MHz processor.                                                                          |  |  |  |

| ZEUS-M128-F32-004-I-R6 <sup>*</sup> | Main features (all other features are included unless otherwise stated):                     |  |  |  |

|                                     | <ul> <li>Industrial temperature range (-40°C to +85°C).</li> </ul>                           |  |  |  |

|                                     | <ul> <li>5V only (No DC/DC PSU).</li> </ul>                                                  |  |  |  |

|                                     | <ul> <li>416MHz processor.</li> </ul>                                                        |  |  |  |

| ZEUS-Mx-Fy-zzz-R6                   | Please note:                                                                                 |  |  |  |

| ZEUS-Mx-Fy-zzz-I-R6 <sup>*</sup>    | <ul> <li>x can be 256, 128 or 64.</li> </ul>                                                 |  |  |  |

|                                     | <ul> <li>y can be 64 or 32.</li> </ul>                                                       |  |  |  |

|                                     | <ul> <li>zzz is a variant number based on different<br/>combinations of features.</li> </ul> |  |  |  |

\* Industrial temperature range: -40°C (-40°F) to +85°C (+185°F). Please contact Eurotech for availability of industrial temperature options.

The ZEUS board is fully RoHS-6 compliant.

For alternative board configurations, please contact Eurotech Sales (see page 125).

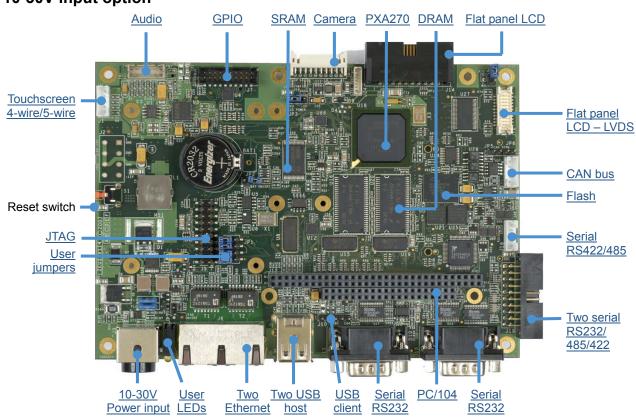

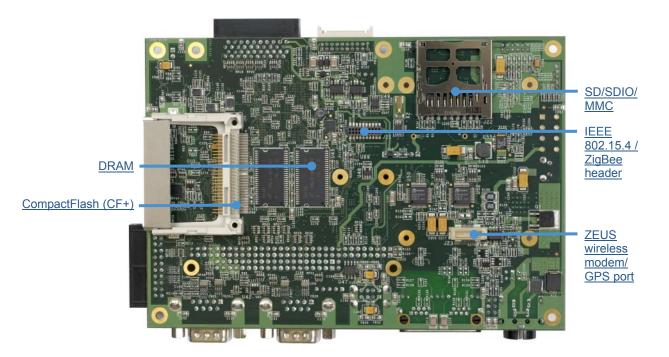

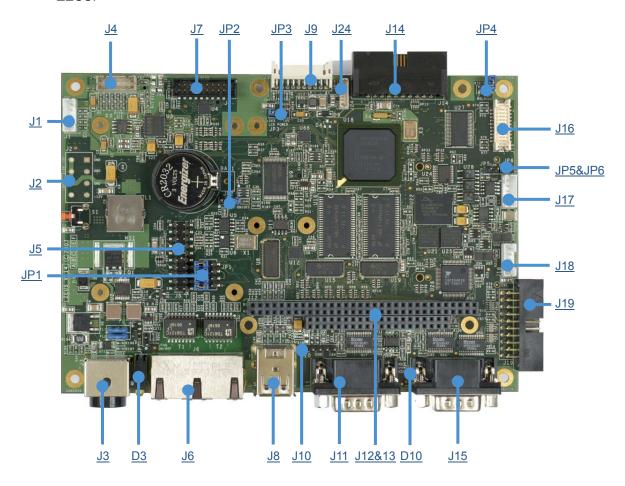

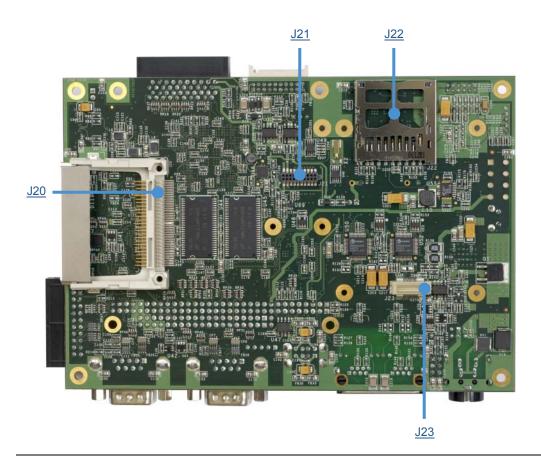

# ZEUS 'at a glance'

# 10-30V input option

# **5V** input option

# **ZEUS** features

# Microprocessor

PXA270 312/416/520MHz processor (520MHz fitted as standard).

#### Cache

• 32K data cache, 32K instruction cache, 2K mini data cache.

# **System memory**

Fixed on-board memory:

64/128/256 MB SDRAM (32-bit wide SDRAM data bus).

# Flash memory

Fixed on-board memory - 32/64MB Flash.

## **SRAM**

256 KB of SRAM battery backed on board.

#### Video

- 18-bit flat panel interface for STN and TFT displays.

- Optional LVDS interface.

# Serial ports

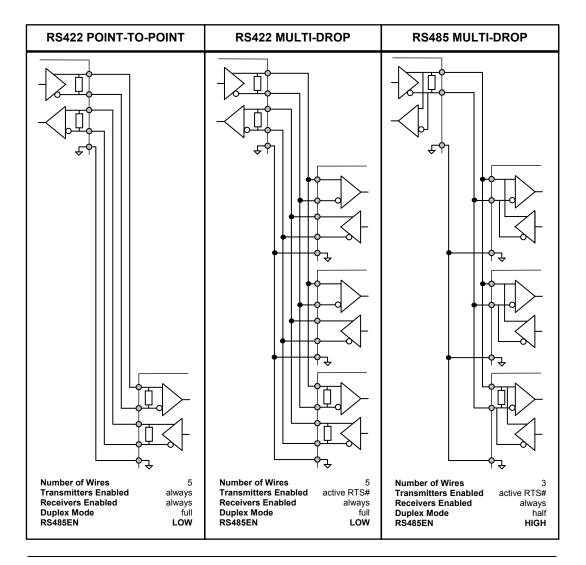

- Four UART fast serial ports 4x 16550 compatible UARTs (921.6Kbaud):

- OneRS422/485 software selectable.

- One RS232/422/485 software selectable.

- Two RS232.

# Wireless support

- GSM/GPRS, iDEN, CDMA modem and GPS using low profile add-on module.

- IEEE802.15.4 / ZigBee wireless interface using low profile add-on module.

## **Network support**

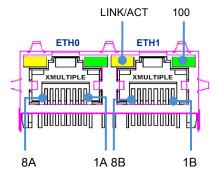

- Two 10/100Base-T Ethernet controllers (Davicom DM9000A).

- On-board dual-port RJ45 jack with LEDs.

- Factory build option for external Power-over-Ethernet (PoE).

# **USB** support

- Two USB 1.1 host controller ports supporting 12MB/s and 1.5MB/s speeds.

- Alternatively, one host channel may be configured as a USB 1.1 client controller port supporting 12MB/s and 1.5MB/s speeds.

- Power switch included on board with 500mA current limit.

- Two USB A-type connectors for host ports.

- · Header for client port.

# **Expansion interfaces**

- CompactFlash CF+ socket to support Type I,II form factor CF+ cards.

- SDIO socket to support MMC/SD/SDIO cards.

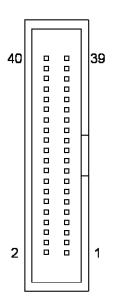

- 16-bit PC/104 interface.

# **Date/time support**

Real time clock – battery backed on-board (external to PXA270).

#### Audio and touchscreen

- Wolfson WM9712L AC'97 compatible CODEC.

- Line in, line out, microphone in, stereo amp out.

- Touchscreen support 4/5-wire analogue resistive.

## **Quick Capture camera interface**

- Intel Quick Capture technology.

- Header connector to a camera image sensor.

# I<sup>2</sup>C bus

Multi-master serial bus, header connection.

# **Configuration EPROM**

I<sup>2</sup>C EPROM for storing configuration data.

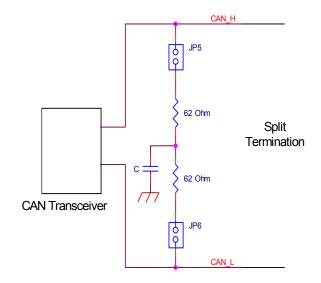

## **CAN** bus

Optional CAN 2.0B protocol controller and optoisolated transceiver.

## Watchdog timer

External to PXA270, generates reset on timeout. Timeout range 1ms-60s.

#### General I/O

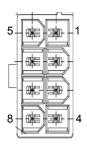

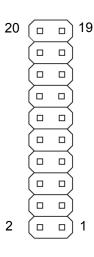

16 general purpose I/O (20-pin header).

# **Temperature sensor**

I<sup>2</sup>C temperature sensor.

## **User LEDs**

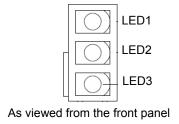

Front panel user LEDs (3x yellow).

# **Test support**

• JTAG interface (standard 20-pin ARM header).

#### Reset

Reset button.

# **Power requirements**

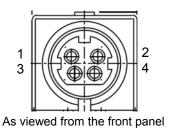

• 5V operation (8-pin ATX style connector) or 10-30V input (front panel DC connector).

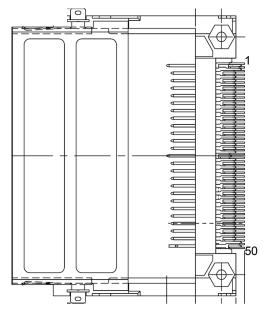

## Mechanical

• EPIC form factor (115mm x 165mm).

# **Environmental**

- Operating temperature:

- Commercial: -20°C (-4°F) to +70°C (+158°F) for speed variants up to 520MHz.

- Industrial: -40°C (-40°F) to +85°C (+185°F) for speed variants up to 416MHz.

- RoHS Directive Compliant (2002/95/EC).

# **ZEUS support products**

The following products support the ZEUS:

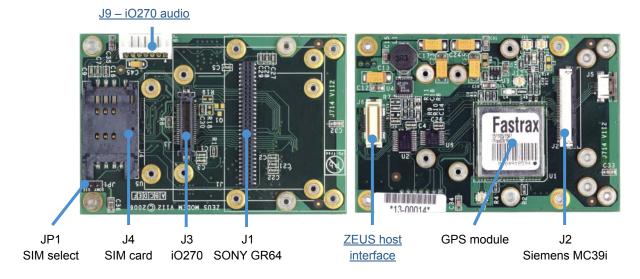

- ZEUS Modem Board 1, a low profile module attached to the solder side of the ZEUS main board. It provides the following wireless connectivity options:

- Quad band GSM/GPRS: Sony Ericsson GR64 or Dual band Siemens MC39i module.

- iDEN: Motorola iO270 module (includes internal GPS receiver).

- GPS: Fastrax iTRAX0312 channel GPS receiver module.

See ZEUS Modem Board 1, page 110, for further details.

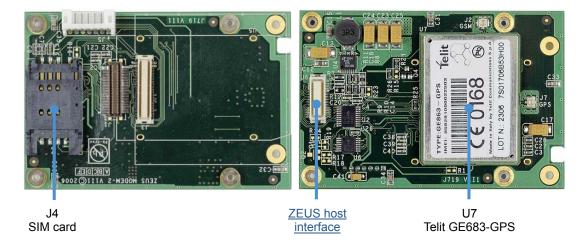

- ZEUS Modem Board 2, a low profile module attached to the solder side of the ZEUS board. It provides the following wireless connectivity:

- Quad band GSM/GPRS: TELIT GE863-GPS module (includes internal GPS receiver).

See ZEUS Modem Board 2, page 110, for further details.

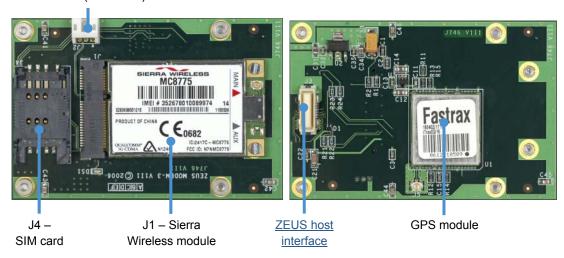

- ZEUS Modem Board 3, a low profile module attached to the solder side of the ZEUS main board. It provides the following wireless connectivity:

- GSM/GPRS: SierraWireless MC8780/MC8775/MC8755 modules.

- CDMA: SierraWireless MC5720/MC5725 modules.

- GPS: Fastrax iTRAX0312 channel GPS receiver module.

See ZEUS Modem Board 3, page 111, for further details.

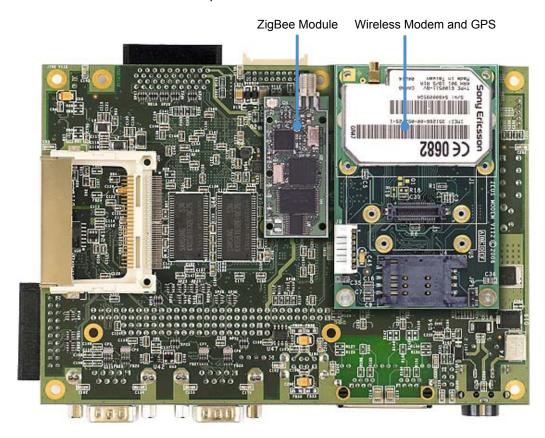

ZigBee module (ZMx), a direct plug-in option for the ZEUS board that provides

ZigBee (see <a href="www.zigbee.org">www.zigbee.org</a>) and IEEE 802.15.4 compatible wireless connectivity.

It provides a fully functioning IEEE802.15.4 / ZigBee controller.

See IEEE802.15.4 / ZigBee module (ZMx), page 35, for further details.

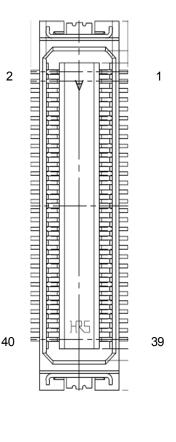

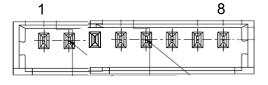

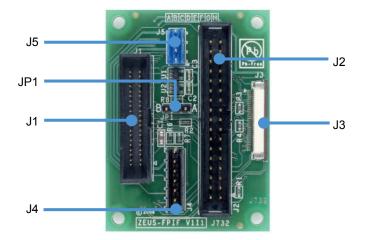

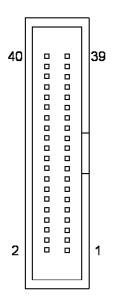

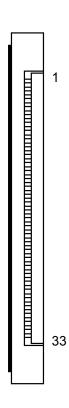

• **ZEUS-FPIF** (Flat Panel Interface), a simple board that enables easy connection between the ZEUS and a variety of LCD flat panel displays.

See ZEUS-FPIF, page 114, for further details.

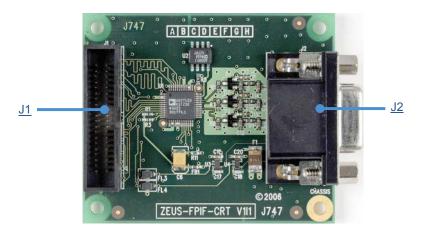

ZEUS-FPIF-CRT, a board that allows the ZEUS to drive a CRT Monitor or an analogue LCD flat panel. Sync on green and composite sync monitors are not supported.

See ZEUS-FPIF-CRT, page 119, for further details.

Contact Eurotech Sales, page  $\underline{125}$ , for further information about any of the above products.

# Product handling and environmental compliance

# **Anti-static handling**

This board contains CMOS devices that could be damaged in the event of static electricity being discharged through them. At all times, please observe anti-static precautions when handling the board. This includes storing the board in appropriate anti-static packaging and wearing a wrist strap when handling the board.

# **Packaging**

Please ensure that, should a board need to be returned to Eurotech, it is adequately packed (preferably in the original packing material).

# **Electromagnetic compatibility (EMC)**

The ZEUS is classified as a component with regard to the European Community EMC regulations and it is the user's responsibility to ensure that systems using the board are compliant with the appropriate EMC standards.

# RoHS compliance

The European RoHS Directive (Restriction on the Use of Certain Hazardous Substances – Directive 2002/95/EC) limits the amount of six specific substances within the composition of the product. The ZEUS and associated accessory products are available as RoHS-6 compliant options and are identified by an -R6 suffix in the product order code. A full RoHS Compliance Materials Declaration Form is included in <a href="Appendix I - RoHS-6 Compliance - Materials Declaration Form">Appendix I - RoHS-6 Compliance - Materials Declaration Form</a>. Further information about RoHS compliance is available on the Eurotech web site at <a href="www.eurotech-ltd.co.uk/RoHS">www.eurotech-ltd.co.uk/RoHS</a> and <a href="www.eurotech-ltd.co.uk/RoHS">WEEE</a>.

Issue E (13

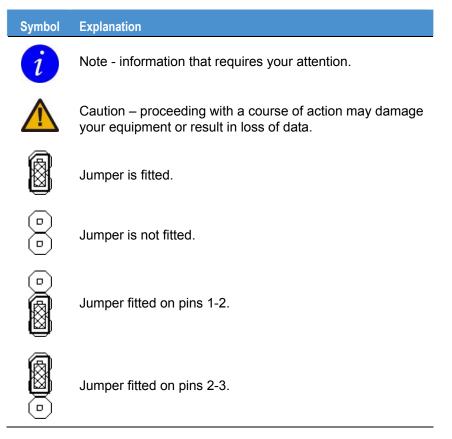

# **Conventions**

The following symbols are used in this guide:

# **Tables**

With tables such as that shown below, the white cells show information relevant to the subject being discussed. Grey cells are not relevant in the current context.

| Byte lane |    |    | Most | sign | ifican | t byte | 9 |   |   |   | l | _east | sign | ifican | t byte      |          |

|-----------|----|----|------|------|--------|--------|---|---|---|---|---|-------|------|--------|-------------|----------|

| Bit       | 15 | 14 | 13   | 12   | 11     | 10     | 9 | 8 | 7 | 6 | 5 | 4     | 3    | 2      | 1           | 0        |

| Field     | -  | -  | -    | -    | -      | -      | - | - | - | - | - | -     | -    | RETRIC | AUTO<br>CLR | R_DIS    |

| Reset     | Х  | Х  | X    | X    | Х      | Х      | X | Х | 0 | 0 | 0 | 0     | 0    | 0      | 0           | 0        |

|           |    |    |      |      |        |        |   |   |   |   |   |       |      |        |             | Relevant |

information

# **Getting started**

A ZEUS Quickstart Manual is provided with each Development Kit to enable you to set up and start using the ZEUS board. Please read the relevant manual and follow the steps explaining how to set up the board. Once you have completed this task, and your ZEUS system is working, you can start adding further peripherals enabling development to begin.

This section explains how to set up and use some of the features of the ZEUS. For more detailed information on any aspect of the board see the section <u>Detailed hardware</u> description, page 17.

# **Using the ZEUS**

# Using the CompactFlash socket

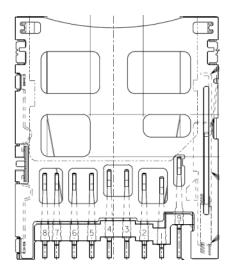

The ZEUS is fitted with a Type I/II CompactFlash socket mounted on the solder side of the board. The socket is connected to Slot 0 of the PXA270 PC card interface. It supports 3.3V Type I and II CompactFlash cards, for both memory and I/O. The ZEUS supports hot swap changeover of the cards and notification of card insertion.

For more details see Expansion interfaces, page 36.

5V CompactFlash cards are not supported.

# Using the serial interfaces (RS232/422/485)

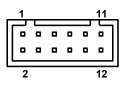

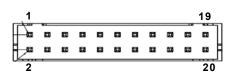

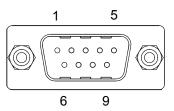

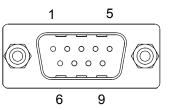

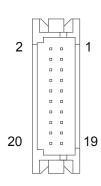

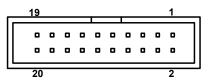

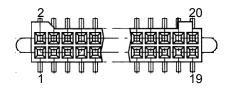

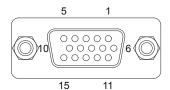

The four standard serial port interfaces on the ZEUS are fully 16550 compatible. Connection to the serial ports is made via two DB9 connectors, a 20-way header and a simple 5 way header. The pin assignment of the 20 way header has been arranged to enable 9-way IDC D-Sub plugs to be connected directly to the cable. See the section J19 — Serial ports — COM3/4, page 80, for pin assignments and connector details.

See the section Serial COM ports, page 47, for further details.

#### Using the audio features

There are four audio interfaces supported on the ZEUS: amp out, line out, line in and microphone. The line in, line out and amp interfaces support stereo signals and the microphone provides a mono input. The amplified output is suitable for driving an  $8\Omega$  load with a maximum power output of 250mW per channel.

Connections are routed to J11. See the sections  $\underline{\text{Audio}}$ , page  $\underline{45}$ , and  $\underline{\text{J4} - \text{Audio}}$  connector, page 71, for further details.

#### Using the USB ports

The standard dual USB type 'A' connector is provided on the front panel. See the sections <u>USB</u>, page 46, and <u>J8 – USB connector</u>, page <u>73</u>, for further details.

Issue E (15

# Using the Ethernet interface

The boot loader configures the Davicom DM9000A 10/100BaseTX Ethernet controller. Connection is made via a dual RJ45 connector. See the sections <u>Ethernet</u>, page  $\underline{47}$ , and  $\underline{J6}$  – <u>Ethernet connector</u>, page  $\underline{72}$ , for further details.

# Using the PC/104 expansion bus

PC/104 modules can be used with the ZEUS to add extra functionality to the system. This interface supports 8/16 bit ISA bus style peripherals.

Eurotech has a wide range of PC/104 modules, which are compatible with the ZEUS. These include modules for digital I/O, analogue I/O and motion control. Please contact Eurotech Sales (see page 125) if a particular interface you require does not appear to be available as these modules are in continuous development.

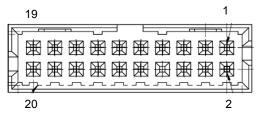

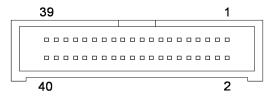

In order to use a PC/104 board with the ZEUS it should be plugged into J12 for 8-bit cards and J12/J13 for 8/16-bit cards. See the sections <u>ZEUS PC/104 interface details</u>, page 38, and J12 & J13 – PC/104 connectors, page 76, for further details.

The ISA interface on the ZEUS does not support DMA, shared interrupts and some access modes. See the section <u>PC/104 interrupts</u>, page <u>39</u>, for details about PC/104 interrupt use.

The ZEUS provides +5V to a PC/104 add-on board via the J12 and J13 connectors. If a PC/104 add-on board requires a +12V supply, then +12V must be supplied to the ZEUS power connector J2 pin 4. If –12V or –5V are required, these must be supplied directly to the PC/104 add-on board.

## **Using the ZEUS Modem Modules**

The ZEUS Modem modules can be used with the ZEUS to add wireless and GPS functionality to the system. Various wireless modems are supported to provide packet data, circuit switched data and voice connectivity on a wireless network. A 12 channel GPS receiver is also available on the ZEUS Modem module. The ZEUS Modem module is fitted on the solder side of the ZEUS board (connector J23).

The FFUART serial port of PXA270 is used to communicate with the wireless modem, and STUART is used to communicate with GPS module. See the sections <u>Wireless modem and GPS receiver</u>, page <u>34</u>, and <u>J23 – Wireless modem/GPS module interface</u>, page <u>83</u>, for further details.

# **Using the ZigBee Module**

The ZEUS ZigBee module can be used with the ZEUS to provide ZigBee (<a href="www.zigbee.org">www.zigbee.org</a>) and IEEE 802.15.4 compatible wireless connectivity. The BTUART serial port of PXA270 is used to communicate with the ZigBee module. The ZigBee module is fitted on the solder side of the ZEUS board (connector J21). For further details, see sections <a href="IEEE802.15.4">IEEE802.15.4</a> / ZigBee module, page 35.

# **Detailed hardware description**

This section provides a detailed description of the functions provided by the ZEUS. This information may be required during development after you have started adding extra peripherals, or are starting to use some of the embedded features.

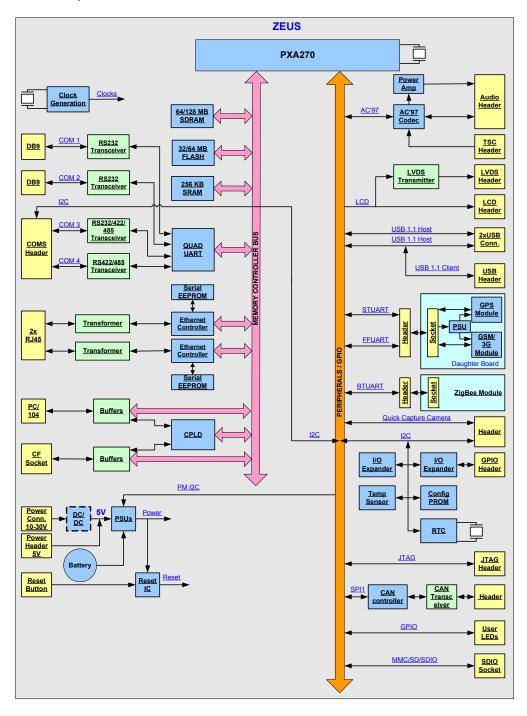

# **ZEUS block diagram**

The following diagram illustrates the functional organization of the ZEUS EPIC single board computer:

# **ZEUS** address map

| PXA270 chip select | Physical address        | Bus width | Description                              |

|--------------------|-------------------------|-----------|------------------------------------------|

| CS0#               | 0x00000000 - 0x03FFFFE  | 16-bit    | Flash memory/Silicon disk                |

| CS1#               | 0x04000000 – 0x07FFFFE  | 16-bit    | Ethernet controller 0                    |

| CS2#               | 0x08000000 – 0x0BFFFFFE | 16-bit    | Ethernet controller 1                    |

| CS3#               | 0x0C000000 – 0x0FFFFFF  | -         | Reserved                                 |

| CS4#               | 0x10000000 – 0x11FFFFE  | 16-bit    | Quad UART                                |

|                    | 0x12000000 – 0x13FFFFE  | 16-bit    | CPLD registers                           |

| CS5#               | 0x14000000 – 0x17FFFFE  | 16-bit    | SRAM                                     |

| -                  | 0x18000000 – 0x1FFFFFF  | -         | Reserved                                 |

| -                  | 0x20000000 – 0x2FFFFFE  | 16-bit    | CompactFlash                             |

| -                  | 0x30000000 - 0x300003FF | 8/16-bit  | PC/104 I/O space                         |

| -                  | 0x30000400 – 0x3BFFFFFF | -         | Reserved                                 |

| -                  | 0x3C000000 - 0x3C1FFFFF | 8/16-bit  | PC/104 memory space                      |

| -                  | 0x3C200000 – 0x3FFFFFFF | -         | Reserved                                 |

| -                  | 0x40000000 – 0x43FFFFFF | 32-bit    | PXA270 peripherals <sup>1</sup>          |

| -                  | 0x44000000 - 0x47FFFFC  | 32-bit    | LCD control registers <sup>1</sup>       |

| -                  | 0x48000000 – 0x4BFFFFC  | 32-bit    | Memory controller registers <sup>1</sup> |

| -                  | 0x4C000000 – 0x4FFFFFC  | 32-bit    | USB host registers <sup>1</sup>          |

| -                  | 0x50000000 – 0x53FFFFC  | 32-bit    | Capture interface registers <sup>1</sup> |

| -                  | 0x54000000 - 0x57FFFFC  | 32-bit    | Reserved                                 |

| -                  | 0x58000000 - 0x5BFFFFC  | 32-bit    | Internal memory control <sup>1</sup>     |

| -                  | 0x5C000000 - 0x5C00FFFC | 32-bit    | Internal SRAM bank 0                     |

| -                  | 0x5C010000 - 0x5C01FFFC | 32-bit    | Internal SRAM bank 1                     |

| -                  | 0x5C020000 – 0x5C02FFFC | 32-bit    | Internal SRAM bank 2                     |

| -                  | 0x5C030000 - 0x5C03FFFC | 32-bit    | Internal SRAM bank 3                     |

| -                  | 0x5C040000 – 0X7FFFFFF  | -         | Reserved                                 |

| SDCS0#             | 0x80000000 – 0x8FFFFFF  | 32-bit    | SDRAM (U2/U3)                            |

| SDCS1#             | 0x90000000 – 0x9FFFFFF  | 32-bit    | SDRAM (U41/U49)                          |

<sup>&</sup>lt;sup>1</sup> Details of the internal registers are in the *Intel PXA27x Processor Family Developer's Manual* on the Development Kit CD.

4

# **UART** and **CPLD** address map

| PXA270 chip select | Physical address        | Bus width | Description             |

|--------------------|-------------------------|-----------|-------------------------|

| CS4#               | 0x10000000 – 0x107FFFE  | 16-bit    | UART 1                  |

|                    | 0x10800000 – 0x10FFFFE  | 16-bit    | UART 2                  |

|                    | 0x11000000 – 0x117FFFE  | 16-bit    | UART 3                  |

|                    | 0x11800000 – 0x11FFFFFE | 16-bit    | UART 4                  |

|                    | 0x12000000              | 16-bit    | REG0 (CPLD Ver/Issue)   |

|                    | 0x12800000              | 16-bit    | REG1 (PC104 IRQ status) |

|                    | 0x13000000              | 16-bit    | REG2 (CF Reset)         |

|                    | 0x13800000              | 16-bit    | REG3 (WD Register)      |

# PXA270 processor

The ZEUS board is based on a PXA270 processor. The PXA270 processor is an integrated system-on-a-chip microprocessor for high performance, low power portable handheld and handset devices. It incorporates the Intel XScale technology with on-the-fly voltage and frequency scaling and sophisticated power management.

The PXA270 processor complies with the ARM Architecture V5TE instruction set (excluding floating point instructions) and follows the ARM programmer's model. The PXA270 processor also supports Intel Wireless MMX integer instructions in applications such as those that accelerate audio and video processing.

The features of the PXA270 processor include:

- Intel XScale core.

- Power management.

- Internal memory 256KB of on-chip RAM.

- Interrupt controller.

- Operating-system timers.

- Pulse-width modulation unit (PWM).

- Real time clock (RTC).

- General-purpose I/O (GPIO).

- Memory controller.

- DMA controller.

- Serial ports:

- 3x UART.

- Fast infrared port.

- I2C bus port.

- AC97 Codec interface.

- I2S Codec Interface.

- USB host controller (2 ports).

- USB client controller.

- 3x synchronous serial ports (SSP).

- LCD panel controller.

- Multimedia card, SD memory card and SDIO card controller.

- Memory stick host controller.

- Mobile scalable link (MSL) interface.

- Keypad interface.

- Universal subscriber identity module (USIM) interface.

- Quick Capture camera interface.

- JTAG interface.

- 356-pin VF-BGA packaging.

The design supports 520MHz, 416MHz and 312MHz speed variants of the PXA270 processor. The standard variant of the ZEUS board is fitted with the 520MHz version of PXA270. The maximum speed available for extended temperature versions of the ZEUS is 416MHz.

A 13MHz external crystal is used to run the PXA270 processor. All other clocks are generated internally in the processor.

The PXA270 processor family provides multimedia performance, low power capabilities and rich peripheral integration. Designed for wireless clients, it incorporates the latest Intel advances in mobile technology over its predecessor, the PXA255 processor. The PXA270 processor features scalability by operating from 104MHz up to 520MHz, providing enough performance for the most demanding control and monitoring applications.

PXA270 is the first Intel Personal Internet Client Architecture (PCA) processor to include Intel Wireless MMX technology, enabling high performance, low power multimedia acceleration with a general-purpose instruction set. Intel Quick Capture technology provides a flexible and powerful camera interface for capturing digital images and video. Power consumption is also a critical component. Wireless Intel SpeedStep technology provides the new capabilities in low power operation.

The processor requires a number of power supply rails. All voltage levels are generated on-board from either the DC/DC PSU or from the single +5V power input. The ZEUS uses a specialized Power Management IC to support Intel SpeedStep technology.

The PXA270 processor is a low power device and does not require a heat sink for operating temperatures up to 85°C (185°F).

# **PXA270 GPIO pin assignments**

The table below summarizes the use of the 118 PXA270 GPIO pins, their direction, alternate function and active level.

# Key:

AF Alternate function. Dir Pin direction.

Active Function active level or edge.

For details of pin states during sleep modes and reset see the Pin Usage table in the *Intel PXA27x Processor Family Electrical, Mechanical and Thermal Specification*.

| GF<br>No | PIO<br>AF | Signal name | Dir    | Active         | Function                       | Wake-up<br>source | See section                                          |

|----------|-----------|-------------|--------|----------------|--------------------------------|-------------------|------------------------------------------------------|

| 0        | 0         | AC97_IRQ    | Input  |                | AC97Interrupt                  | ✓                 | Audio, page 45                                       |

| 1        | 0         | DS_WAKEUP   | Input  | <b>¬</b> _     | Reset in case of power failure | ✓                 |                                                      |

| 3        | 0         | PWR_SCL     | Output |                | PXA270 Power                   |                   | Power 10                                             |

| 4        | 0         | PWR_SDA     | Bidir. |                | Manager I <sup>2</sup> C       |                   | management IC,<br>page <u>57</u>                     |

| 5        | N/A       | PWR_CAP0    | Power  |                |                                |                   |                                                      |

| 6        | N/A       | PWR_CAP1    | Power  |                | Dedicated function - To        |                   | NI/A                                                 |

| 7        | N/A       | PWR_CAP2    | Power  |                | achieve low power during sleep |                   | N/A                                                  |

| 8        | N/A       | PWR_CAP3    | Power  |                |                                |                   |                                                      |

| 9        | 0         | UART_INTA   | Input  |                | UART 1 Interrupt               | ✓                 |                                                      |

| 10       | 0         | UART_INTB   | Input  |                | UART 2 Interrupt               | ✓                 | Serial COM ports, page 47                            |

| 11       | 0         | UART_INTD   | Input  | _ <del>_</del> | UART 4 Interrupt               | ✓                 | page <u>+r</u>                                       |

| 12       | 0         | UART_INTC   | Input  |                | UART 3 Interrupt               | ✓                 |                                                      |

| 13       | 0         | USER_LINK1  | Input  |                | User configurable Input        | ✓                 | <u>JP1 – User</u><br><u>jumpers</u> , page <u>85</u> |

|          |           |             |        |                |                                |                   | continued                                            |

| GF<br>No | PIO<br>AF | Signal name | Dir    | Active   | Function                                             | Wake-up<br>source | See section                                     |

|----------|-----------|-------------|--------|----------|------------------------------------------------------|-------------------|-------------------------------------------------|

| 14       | 0         | ETH0_IRQ#   | Input  | ¬_       | Ethernet 0 Interrupt                                 | ✓                 | Ethernet, page 47                               |

| 15       | 2         | ETH_CS1#    | Output | Low      | Chip Select 1 –<br>Ethernet 0                        |                   | Ethernet, page 47                               |

| 16       | 2         | PWM0        | Output | er       | Backlight Brightness<br>On/Off or variable if<br>PWM |                   | LCD backlight<br>brightness control,<br>page 44 |

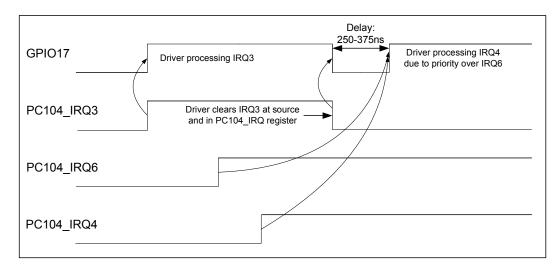

| 17       | 0         | ISA_IRQ     | Input  |          | 'OR' of PC/104<br>interrupts                         | ✓                 | PC/104 interrupts, page 39                      |

| 18       | 0         | RESERVED    |        |          |                                                      |                   |                                                 |

| 19       | 0         | BKLEN       | Output | High     | LCD Backlight Enable                                 |                   | LCD logic and backlight power, page 43          |

| 20       | 0         | ISA_RST#    | Input  | <b>_</b> | PC104 Reset Indication (IRQ)                         |                   | ZEUS PC/104<br>interface details,<br>page 38    |

| 21       | 0         | LVDS_EN     | Output | High     | LVDS Transceiver<br>Enable                           |                   | LVDS interface, page 44                         |

| 22       | 0         | USB_PWE2    | Output | High     | USB Port 2 Power<br>Enable                           |                   | USB, page 46                                    |

| 23       | 1         | CIF_MCLK    | Output | NA       | Camera Interface<br>Master Clock                     |                   |                                                 |

| 24       | 1         | CIF_FV      | Input  | NA       | Camera Interface<br>Frame Sync -Vertical             |                   | Quick Capture                                   |

| 25       | 1         | CIF_LV      | Input  | NA       | Camera Interface Line<br>Sync - Horizontal           |                   | camera interface,<br>page <u>54</u>             |

| 26       | 2         | CIF_PCLK    | Input  | NA       | Camera Interface Pixel Clock                         |                   |                                                 |

| 27       | 0         | PTT         | Input  | High     | Push To Talk                                         |                   | ZEUS Modem-1, page 110                          |

| 28       | 1         | AC97_BITCLK | Input  |          | AC97 BIT CLOCK                                       |                   |                                                 |

| 29       | 1         | AC97_DIN    | Input  | NA       | AC97 DATA IN                                         |                   | Audio, page 45                                  |

| 30       | 2         | AC97_DOUT   | Output | NA       | AC97 DATA OUT                                        |                   | Addio, page 40                                  |

| 31       | 2         | AC97_SYNC   | Output |          | AC97 SYNC                                            |                   |                                                 |

|          |           |             |        |          |                                                      |                   | continued                                       |

| GP<br>No | PIO<br>AF | Signal name | Dir    | Active   | Function                         | Wake-up<br>source | See section                                    |

|----------|-----------|-------------|--------|----------|----------------------------------|-------------------|------------------------------------------------|

| 32       | 2         | MMCLK       | Output | NA       | SDIO Clock                       |                   | SDIO, page 36                                  |

| 33       | 2         | SRAM_CS5#   | Output | Low      | Chip Select 5 - SRAM             |                   | Static RAM, page 33                            |

| 34       | 1         | GSM_FFRXD   | Input  | NA       | Modem Receive Data               |                   | Wireless modem<br>and GPS receiver,<br>page 34 |

| 35       | 0         | CF_CD#      | Input  | <b>_</b> | Compact Flash Card<br>Detect IRQ | ✓                 | CompactFlash, page 37                          |

| 36       | 1         | GSM_FFDCD#  | Input  | NA       | Modem Data Carrier<br>Detect     |                   |                                                |

| 37       | 1         | GSM_FFDSR#  | Input  | NA       | Modem Data Sender<br>Ready       |                   |                                                |

| 38       | 1         | GSM_FFRI#   | Input  | NA       | Modem Ring Indicator             |                   | Wireless modem                                 |

| 39       | 2         | GSM_FFTXD   | Output | NA       | Modem Transmit Data              |                   | and GPS<br>receiver, page 34                   |

| 40       | 2         | GSM_FFDTR#  | Output | NA       | Modem Data Terminal<br>Ready     |                   |                                                |

| 41       | 2         | GSM_FFRTS#  | Output | NA       | Modem Request To<br>Send         |                   |                                                |

| 42       | 1         | ZB_BTRXD    | Input  | NA       | ZigBee Receive Data              |                   |                                                |

| 43       | 2         | ZB_BTTXD    | Output | NA       | ZigBee Transmit Data             |                   | IEEE802.15.4 /                                 |

| 44       | 1         | ZB_BTCTS#   | Input  | NA       | ZigBee Clear To Send             |                   | ZigBee module,<br>page <u>35</u>               |

| 45       | 2         | ZB_BTRTS#   | Output | NA       | ZigBee Request To<br>Send        |                   | . 5                                            |

| 46       | 2         | GPS_STDRXD  | Input  | NA       | GPS Receive Data                 |                   | Wireless modem                                 |

| 47       | 1         | GPS_STDTXD  | Output | NA       | GPS Transmit Data                |                   | and GPS<br>receiver, page 34                   |

| 48       | 2         | CB_POE#     | Output | Low      | Card Bus Output<br>Enable        |                   |                                                |

| 49       | 2         | CB_PWE#     | Output | Low      | Card Bus Write Enable            |                   | Expansion interfaces, page                     |

| 50       | 2         | CB_PIOR#    | Output | Low      | Card Bus I/O Read                |                   | 36                                             |

| 51       | 2         | CB_PIOW#    | Output | Low      | Card Bus I/O Write               |                   |                                                |

|          |           |             |        |          |                                  |                   | continued                                      |

| GP<br>No | PIO<br>AF | Signal name | Dir    | Active | Function                                        | Wake-up<br>source | See section                   |

|----------|-----------|-------------|--------|--------|-------------------------------------------------|-------------------|-------------------------------|

| 52       | 0         | MMC_WP      | Input  | Low    | SDIO Write Protect<br>Status                    |                   | SDIO, page 36                 |

| 53       | 0         | MMC_CD      | Input  |        | SDIO Card Detect IRQ                            | ✓                 |                               |

| 54       | 2         | CB_PCE2#    | Output | Low    | Card Bus High Byte<br>Enable                    |                   |                               |

| 55       | 2         | CB_PREG#    | Output | Low    | Card Bus Register<br>Space Select               |                   | Expansion<br>interfaces, page |

| 56       | 1         | CB_WAIT#    | Input  | Low    | Card Bus WAIT#                                  |                   | <u>36</u>                     |

| 57       | 1         | CB_PIOIS16# | Input  | Low    | Card Bus IOIS16#                                |                   |                               |

| 58       | 2         | LCD_D0      | Output | NA     | LCD Data Bit 0                                  |                   |                               |

| 59       | 2         | LCD_D1      | Output | NA     | LCD Data Bit 1                                  |                   |                               |

| 60       | 2         | LCD_D2      | Output | NA     | LCD Data Bit 2                                  |                   |                               |

| 61       | 2         | LCD_D3      | Output | NA     | LCD Data Bit 3                                  |                   |                               |

| 62       | 2         | LCD_D4      | Output | NA     | LCD Data Bit 4                                  |                   |                               |

| 63       | 2         | LCD_D5      | Output | NA     | LCD Data Bit 5                                  |                   |                               |

| 64       | 2         | LCD_D6      | Output | NA     | LCD Data Bit 6                                  |                   |                               |

| 65       | 2         | LCD_D7      | Output | NA     | LCD Data Bit 7                                  |                   |                               |

| 66       | 2         | LCD_D8      | Output | NA     | LCD Data Bit 8                                  |                   |                               |

| 67       | 2         | LCD_D9      | Output | NA     | LCD Data Bit 9                                  |                   |                               |

| 68       | 2         | LCD_D10     | Output | NA     | LCD Data Bit 10                                 |                   | Flat panel display,           |

| 69       | 2         | LCD_D11     | Output | NA     | LCD Data Bit 11                                 |                   | page <u>40</u>                |

| 70       | 2         | LCD_D12     | Output | NA     | LCD Data Bit 12                                 |                   |                               |

| 71       | 2         | LCD_D13     | Output | NA     | LCD Data Bit 13                                 |                   |                               |

| 72       | 2         | LCD_D14     | Output | NA     | LCD Data Bit 14                                 |                   |                               |

| 73       | 2         | LCD_D15     | Output | NA     | LCD Data Bit 15                                 |                   |                               |

| 74       | 2         | LCD_FCLK    | Output | NA     | LCD Frame Clock (STN)<br>/ Vertical Sync (TFT)  |                   |                               |

| 75       | 2         | LCD_LCLK    | Output | NA     | LCD Line Clock (STN) /<br>Horizontal Sync (TFT) |                   |                               |

| 76       | 2         | LCD_PCLK    | Output | NA     | LCD Pixel Clock (STN)<br>/ Clock (TFT)          |                   |                               |

| 77       | 2         | LCD_BIAS    | Output | NA     | LCD Bias (STN) / Data<br>Enable (TFT)           |                   |                               |

|          |           |             |        |        |                                                 |                   | continued                     |

| GF<br>No | PIO<br>AF | Signal name      | Dir    | Active   | Function                             | Wake-up<br>source | See section                                          |

|----------|-----------|------------------|--------|----------|--------------------------------------|-------------------|------------------------------------------------------|

| 78       | 2         | ETH_CS2#         | Output | NA       | Chip Select 2 - Ethernet 1           |                   | Ethernet, page 47                                    |

| 79       | 1         | CB_PSKTSEL       | Output | NA       | Card Bus Socket Select               |                   | Expansion interfaces, page 36                        |

| 80       | 2         | CPLD_CS4#        | Output | Low      | Chip Select 4 –<br>UART/CPLD         |                   | UART and CPLD<br>address map,<br>page 19             |

| 81       | 1         | SPI_TXD3         | Output | NA       | SPI Transmit Data                    |                   |                                                      |

| 82       | 1         | SPI_RXD3         | Input  | NA       | SPI Receive Data                     |                   | CAN bus, page                                        |

| 83       | 1         | SPI_CS3#         | Output | Low      | SPI Chip Select                      |                   | <u>52</u>                                            |

| 84       | 1         | SPI_CLK3         | Output | NA       | SPI Clock                            |                   |                                                      |

| 85       | 1         | CB_PCE1#         | Output | Low      | Card Bus Low Byte<br>Enable          |                   | Expansion<br>interfaces, page<br>36                  |

| 86       | 2         | LCD_D16          | Output | NA       | LCD Data Bit 16                      |                   | Flat panel display,                                  |

| 87       | 2         | LCD_D17          | Output | NA       | LCD Data Bit 17                      |                   | page <u>40</u>                                       |

| 88       | 0         | USB_OC1#         | Input  | <b>—</b> | USB Port 1 Over<br>Current Detection |                   | <u>USB</u> , page <u>46</u>                          |

| 89       | 0         | USB_PWE1         | Output | High     | USB Port 1 Power<br>Enable           |                   | <u>505</u> , page <u>10</u>                          |

| 90       | 3         | CIF_DD4          | Input  | NA       | Camera Interface Data<br>4           |                   | Quick Capture<br>camera interface,<br>page <u>54</u> |

| 91       | 0         | EX_GPIO_IRQ<br># | Input  | <b>¬</b> | External GPIO Interrupt              | ✓                 | External General purpose I/O, page 54                |

| 92       | 1         | MMDAT0           | Bidir. | NA       | SDIO Data 0                          |                   | Expansion<br>interfaces, page<br>36                  |

| 93       | 2         | CIF_DD6          | Input  | NA       | Camera Interface Data<br>6           |                   | Quick Capture                                        |

| 94       | 2         | CIF_DD5          | Input  | NA       | Camera Interface Data 5              |                   | camera interface,<br>page <u>54</u>                  |

| 95       | 1         | AC97_RST#        | Output | Low      | AC97 Reset                           |                   | Audio, page 45                                       |

| 96       | 0         | OVERTEMP         | Input  |          | Temperature Sensor<br>Overtemp IRQ   |                   | Temperature<br>sensor, page <u>55</u>                |

|          |           |                  |        |          |                                      |                   | continued                                            |

| GPI<br>No | IO<br>AF | Signal name Dir Active Function |        | Function                     | Wake-up<br>source                       | See section |                                                       |

|-----------|----------|---------------------------------|--------|------------------------------|-----------------------------------------|-------------|-------------------------------------------------------|

| 97        | 0        | CF_PWEN                         | Output | High                         | Compact Flash Power                     | Source      | CompactFlash, page 37                                 |

| 98        | 2        | CIF_DD0                         | Input  | NA                           | Camera Interface Data                   |             | Quick Capture camera interface, page 54               |

| 99        | 0        | CF_RDY                          | Input  | NA                           | Compact Flash<br>Ready/Busy Status Flag |             | CompactFlash, page 37                                 |

| 100       | 3        | GSM_FFCTS#                      | Input  | NA                           | Modem Clear To Send                     |             | Wireless modem<br>and GPS receiver,<br>page <u>34</u> |

| 101       | 0        | LCD_EN                          | Output | High                         | LCD Logic Supply<br>Enable              |             | Flat panel display, page 40                           |

| 102       | 0        | USER_LINK2                      | Input  | NA                           | User Configurable                       | ✓           | <u>JP1 – User</u><br><u>jumpers, page 85</u>          |

| 103       | 1        | CIF_DD3                         | Input  | NA                           | Camera Interface Data 3                 |             |                                                       |

| 104       | 1        | CIF_DD2                         | Input  | NA                           | Camera Interface Data 2                 |             |                                                       |

| 105       | 1        | CIF_DD1                         | Input  | NA                           | Camera Interface Data<br>1              |             | Quick Capture                                         |

| 106       | 1        | CIF_DD9                         | Input  | put NA Gamera Interface Data |                                         |             | camera interface,<br>page <u>54</u>                   |

| 107       | 1        | CIF_DD8                         | Input  | NA                           | Camera Interface Data 8                 |             |                                                       |

| 108       | 1        | CIF_DD7                         | Input  | NA                           | Camera Interface Data 7                 |             |                                                       |

| 109       | 1        | MMDAT1                          | Bidir. | NA                           | SDIO Data 1                             |             |                                                       |

| 110       | 1        | MMDAT2                          | Bidir. | NA                           | SDIO Data 2                             |             | Expansion                                             |

| 111       | 1        | MMDAT3                          | Bidir. | NA                           | SDIO Data 3                             |             | <u>interfaces</u> , page <u>36</u>                    |

| 112       | 1        | MMCMD                           | Bidir. | NA                           | SDIO Command                            |             |                                                       |

| 113       | 0        | ETH1_IRQ#                       | Input  | <b>_</b>                     | Ethernet 1 Interrupt                    | ✓           | Ethernet, page 47                                     |

| 114       | 0        | USB_OC2#                        | Input  | <b>_</b>                     | USB Port 2 Overcurrent<br>Detection IRQ |             | USB, page 46                                          |

| 115       | 0        | IG_FAIL                         | Input  |                              | Ignition Fail IRQ                       |             | Power supplies, page <u>56</u>                        |

| 116       | 0        | CAN_IRQ#                        | Input  | 7_                           | CAN Bus Interrupt                       | ✓           | CAN bus, page <u>52</u>                               |

| 117       | 1        | I2C _SCL                        | Output | NA                           | I2C Clock                               |             | 120.1                                                 |

| 118       | 1        | I2C _SDA                        | Bidir. | NA                           | I2C Data                                |             | I <sup>2</sup> C bus, page <u>53</u>                  |

# Interrupt assignments

# **Internal interrupts**

For details on the PXA270 interrupt controller and internal peripheral interrupts please see the *Intel PXA27x Processor Family Developer's Manual* on the Development Kit CD.

# **External interrupts**

The following table lists the PXA270 signal pins used for external interrupts:

| PXA270 Pin | Signal name | Peripheral         | Wake-up | Active           |

|------------|-------------|--------------------|---------|------------------|

| GPIO0      | AC97_IRQ    | Audio              | ✓       |                  |

| GPIO1      | GPIO_IRQ#   | External GPIO      | ✓       | <b>—</b>         |

| GPIO9      | UART_INTA   | UART 1             | ✓       |                  |

| GPIO10     | UART_INTB   | UART 2             | ✓       |                  |

| GPIO11     | UART_INTD   | UART 4             | ✓       |                  |

| GPIO12     | UART_INTC   | UART 3             | ✓       |                  |

| GPIO13     | USER_LINK1  | User defined       | ✓       | User defined     |

| GPIO14     | ETH0_IRQ#   | Ethernet 0         | ✓       | <b>-</b>         |

| GPIO17     | ISA_IRQ     | PC/104             | ✓       |                  |

| GPIO20     | ISA_RST#    | PC/104             |         |                  |

| GPIO35     | CF_CD#      | CompactFlash       | ✓       | <b>—</b>         |

| GPIO53     | MMC_CD      | SDIO               | ✓       |                  |

| GPIO88     | USB_OC1#    | USB1               |         | 7_               |

| GPIO91     | USER_LINK2  | User defined       | ✓       | User defined     |

| GPIO96     | OVERTEMP    | Temperature sensor |         |                  |

| GPIO99     | CF_RDY      | CompactFlash       |         | Ready = _ Busy = |

| GPIO102    | USER_LINK2  | User defined       | ✓       | User defined     |

| GPIO113    | ETH1_IRQ#   | Ethernet 1         | ✓       | ¬_               |

| GPIO114    | USB_OC2#    | USB2               |         | <b>-</b>         |

| GPIO115    | IG_FAIL#    | PSU (10-30V)       |         | <b>—</b>         |

| GPIO116    | CAN_IRQ#    | CAN Bus            | ✓       | 7_               |

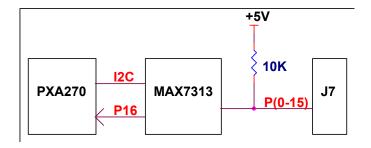

# On-Board GPIO expanders pin assignments

Two GPIO expanders (MAX7313) are used to provide additional GPIOs for use with different on-board peripherals. The GPIO expanders are connected to the I<sup>2</sup>C bus of PXA270 and are accessible through I<sup>2</sup>C bus addresses 0x21 and 0x22.

The following tables summarize the use of the 17 GPIO pins of MAX7313 on ZEUS board, and indicate their direction and active level.

Expander 1 - I2C Address 0x21

| GPIO  | Signal name                                          | Dir    | Active              | Function                 | Power-up state | See section                           |  |  |  |  |

|-------|------------------------------------------------------|--------|---------------------|--------------------------|----------------|---------------------------------------|--|--|--|--|

| 0     | U3_RS232EN                                           | Output | High                | UART3 RS232 enable       | PU             | COM3 –                                |  |  |  |  |

| 1     | U3_RS422EN                                           | Output | High                | UART3 RS422 enable       | PU             | RS232/RS485/RS4                       |  |  |  |  |

| 2     | U3_TERM#                                             | Output | Low                 | UART3 termination enable | PU             | 22 interface, page 48                 |  |  |  |  |

| 3     | USER_LED1<br>#                                       | Output | Low                 | User LED 1               | PU             |                                       |  |  |  |  |

| 4     | USER_LED2<br>#                                       | Output | Low                 | User LED 2               | PU             | <u>User LEDs</u> , page <u>88</u>     |  |  |  |  |

| 5     | USER_LED3<br>#                                       | Output | Low                 | User LED 3               | PU             |                                       |  |  |  |  |

| 6     | USER_LINK3                                           | Input  | NA                  | User jumper 3            | Jumper         | JP1 – User jumpers,<br>page <u>85</u> |  |  |  |  |

| 7     | NOT USED                                             |        |                     |                          | PU             |                                       |  |  |  |  |

| 8     | GSM_ON                                               | Output | See note<br>1 below | Modem enable             | OD             |                                       |  |  |  |  |

| 9     | GSM_STS                                              | Input  | High                | Modem ON/OFF status      | Low            | Wireless modem                        |  |  |  |  |

| 10    | GPS_ON                                               | Output | High                | GPS module enable        | PU             | and GPS receiver, page 34             |  |  |  |  |

| 11    | GPS_PSUON                                            | Input  | NA                  | Not Used                 | PU             | page <u>o+</u>                        |  |  |  |  |

| 12    | GPS_BOOT                                             | Input  | NA                  | Not Used                 | OD             |                                       |  |  |  |  |

| 13    | GPS_PPS                                              | Input  | NA                  | GPS Pulse Per Second     | -              |                                       |  |  |  |  |

| 14    | USER_LINK4                                           | Input  | NA                  | User jumper 4            | Jumper         | JP1 – User<br>jumpers, page <u>85</u> |  |  |  |  |

| 15    | U4_RS485EN                                           | Output | High                | UART4 RS485 enable       | PU             | COM4 –                                |  |  |  |  |

| 16    | U4_TERM#                                             | Output | Low                 | UART4 termination enable | PU             | RS422/485<br>interface, page 49       |  |  |  |  |

| Key:  | ,                                                    |        |                     |                          |                |                                       |  |  |  |  |

| Dir - | Pin direction Active - Function active level or edge |        |                     |                          |                |                                       |  |  |  |  |

Function active level or edge

PU On-board 10K pull-up OD -Open Drain

Please see the datasheet of the particular module used.

Expander 2 - I2C Address 0x22

| GPIO  | Signal name        | Dir    | Active | Function                                       | Power-up state | See section                                       |

|-------|--------------------|--------|--------|------------------------------------------------|----------------|---------------------------------------------------|

| 0     | CLK_SHDN#          | Output | Low    | Clock Synthesizer<br>Shutdown                  | PU             | Clock generator power management, page 64         |

| 1     | LVDS_FES#          | Output | Low    | LVDS Falling Edge<br>Strobe                    | PU             | LVDS interface, page 44                           |

| 2     | CAN_SHDN           | Output | High   | CAN Transceiver shutdown                       | PU             | CAN bus, page 52                                  |

| 3     | U1_RS232_SH<br>DN# | Output | Low    | COM1 RS232<br>transceiver<br>shutdown          | PU             | COM Ports power                                   |

| 4     | U2_RS232_SH<br>DN# | Output | Low    | COM2 RS232<br>transceiver<br>shutdown          | PU             | management, page 65                               |

| 5     | U3_RS485_SL<br>O#  | Output | Low    | COM3 RS485<br>transceiver slew<br>rate control | PU             | COM3 –<br>RS232/RS485/RS422<br>interface, page 48 |

| 6     | U4_RS485_SL<br>O#  | Output | Low    | COM4 RS485<br>transceiver slew<br>rate control | PU             | COM4 – RS422/485<br>interface, page 49            |

| 7     | NOT USED           |        |        |                                                | PU             |                                                   |

| 8-11  | ISS [0-3]          | Inputs | NA     | PCB Issue Number                               |                |                                                   |

| 12-15 | VER [0-3]          | Inputs | NA     | PCB Version<br>Number                          |                |                                                   |

## Real time clock

The ZEUS uses an external real time clock (RTC) (Intersil ISL1208) to store the date and time, and provide power management events. The RTC is connected to the I<sup>2</sup>C bus of the PXA270 processor and is accessible through I<sup>2</sup>C bus address 0x6F. The RTC is battery backed.

The accuracy of the RTC is based on the operation of the 32.768 KHz watch crystal. The calibration tolerance is  $\pm 20$ ppm, which provides an accuracy of +/-1 minute per month when the board is operated at an ambient temperature of +25°C (+77°F). When the board is operated outside this temperature the accuracy may be degraded by -0.035ppm/  $^{\circ}$ C²  $\pm 10\%$  typical. The watch crystal's accuracy will age by  $\pm 3$ ppm max in the first year, then  $\pm 1$ ppm max in the year after, and logarithmically decrease in subsequent years.

The Intersil ISL1208 RTC provides the following basic functions:

- Real time clock/calendar:

- Tracks time in hours, minutes and seconds.

- Day of the week, day, month and year.

- Single alarm:

- Settable to the second, minute, hour, day of the week, day or month.

- Single event or pulse interrupt mode.

- 2 bytes battery-backed user SRAM.

- I<sup>2</sup>C interface.

PXA270 has an internal real time clock, which doesn't keep time after hardware reset, and should only be used as a wake-up source from deep-sleep.

Issue E (37

# Watchdog timer

The ZEUS uses an external watchdog timer (MAX6369) which can be used to protect against erroneous software. This is a programmable watchdog timer that can be adjusted for timeout periods of 1ms, 10ms, 30ms, 100ms, 1s, 10s and 60s. The board is reset when timeout occurs. The MAX6369 watchdog timer can be programmed using the WD setup register provided within the CPLD. The register is memory mapped (accessible through CS5#). The WDT is disabled upon reset, and remains so until enabled by the software.

The following table shows the WD setup register bit definitions:

# Watchdog Register [REG3]

| Bits | Description                                                                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4  | Not used.                                                                                                                                                                                                                                                             |

| 3    | WDI: Watchdog Input. If WDI remains either high or low for the duration of the watchdog timeout period ( $t_{WD}$ ), WDT triggers a reset pulse. The internal watchdog timer clears whenever a reset pulse is asserted or whenever WDI sees a rising or falling edge. |

| 2:0  | WDSET[2:0] – watchdog enable / timeout period setup bits.                                                                                                                                                                                                             |

Hex Offset Address: 0x13800000

Reset Hex Value: 0x03

Access: Read/write

For further details, see the *Intel PXA27x Processor Family Developer's Manual* on the Development Kit CD.

# Memory

The ZEUS has four types of memory fitted:

- 32 or 64MB resident Flash disk containing:

- Boot loader to boot operating system.

- Operating system.

- Application images.

- 64, 128 or 256MB of SDRAM for system memory.

- Static RAM, as follows:

- 256KB of SRAM internal to PXA270.

- 256KB of SRAM external to PXA270 (battery backed).

- 128 bytes of configuration EEPROM on the I<sup>2</sup>C bus.

# Flash memory

The ZEUS supports 32MB or 64MB of Spansion (AMD) MirrorBit Flash memory for the boot loader, OS and application images. The Flash memory is arranged as 128Mbit x 16-bit (32MB device) or as 256Mbit x 16-bit (64MB device).

The Flash memory array is divided into equally sized symmetrical blocks that are 64-Kword in size (128KB) sectors. A 256Mbit device contains 256 blocks, and a 512Mbit device contains 512 blocks.

Whenever the Flash memory is accessed the 'Flash' access LED is illuminated.

#### **SDRAM**

There are two standard memory configurations supported by the ZEUS: 64MB or 128MB of SDRAM located in banks 0 and 1. The SDRAM is configured as 16MB x 32-bit (64MB), or 32MB x 32-bit (128MB). 64MB configuration is using 2 devices, and 128MB configuration is using 4 devices, each with 4 internal banks of 4MB x 16-bit. Optional 256MB configuration is using 4 devices, each with 4 internal banks of 8MB x 16-bit.

These are surface mount devices soldered to the board. The size of memory fitted to the board is detected by software to configure the SDRAM controller accordingly.

The SDRAM memory controller is set to run at frequency of 104MHz.

#### Static RAM

The PXA270 processor provides 256KB of internal memory-mapped SRAM. The SRAM is divided into four banks, each consisting of 64KB.

The ZEUS also has an external 256KB SRAM device fitted, arranged as 256Kbit x 8-bits. Access to the device is on 16-bit boundaries, whereby the least significant byte is the SRAM data and the 8-bits of the most significant byte are 'don't care' bits. The reason for this is that the PXA270 is not designed to interface to 8-bit peripherals. This arrangement is summarized in the following data bus table:

| Most significant byte      |    |    | Lea | st sign | ifican | byte |    |    |    |

|----------------------------|----|----|-----|---------|--------|------|----|----|----|

| D15 D14 D13 D12 D11 D10 D9 | D8 | D7 | D6  | D5      | D4     | D3   | D2 | D1 | D0 |

| Don't Care                 |    |    |     | SRAI    | И Dat  | а    |    |    |    |

The external SRAM is non-volatile while the on-board coin cell battery is fitted.

# **Configuration EEPROM**

The configuration EEPROM is interfaced directly to PXA270's I<sup>2</sup>C controller. It is a Microchip 24AA01 1Kbit EEPROM organized as one block of 128 x 8-bit memory.

The configuration EEPROM is addressable at I<sup>2</sup>C serial bus address 0x50 and is accessed in fast-mode operation at 400KB/s.

Issue E (33)

# Wireless support

The ZEUS can support various wireless modems, GPS functionality and an IEEE802.15.4 / ZigBee wireless sensor network interface. This is achieved using two optional add-on modules. GPS and cellular functionality are integrated on a single module (ZEUS Modem-n) while the IEEE802.15.4 / ZigBee port is provided by a separate module. Other cellular wireless modems such as EVDO, EDGE or satellite modems may be supported via this interface. Please contact Eurotech Sales (see page 125) for more information about the available options.

#### Wireless modem and GPS receiver

Various wireless modems are supported to provide packet data, circuit switched data and voice connectivity on a wireless network. ZEUS also provides complete GPS functionality including position, velocity and time (PVT). The ZEUS modem module is fitted on the solder side of the ZEUS board (connector J23).

The wireless modem is driven by the FFUART serial port (within the PXA270), while the GPS module uses the STUART serial interface (Rx/Tx only). For the connector details, see the section <u>J23 – Wireless modem/GPS module interface</u>, page <u>83</u>.

There are also a number of control/status GPIO signals connected to J23. They can be accessed through a GPIO Expander MAX7313. See the section On-Board GPIO expanders pin assignments, page 29.

ZEUS Modem-1 supports the following modules:

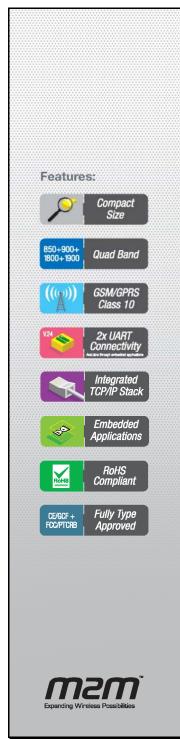

- Sony Ericsson GR64, a quad-band (850/900/1800/1900) version of GR47/48.

Functionally comparable to the Sony Ericsson GR47/GR48 devices, the GR64 offers a broad range of voice and data features. The integrated TCP/IP stack enables effective use of GPRS. For further details see <a href="Sony Ericsson GR64">Sony Ericsson GR64</a>, page 96.

- Siemens MC35i/39i, a dual-band GSM/GPRS module (EGSM 900/1800MHz). For further details see <u>Siemens MC35i/39i</u>, page <u>98</u>.

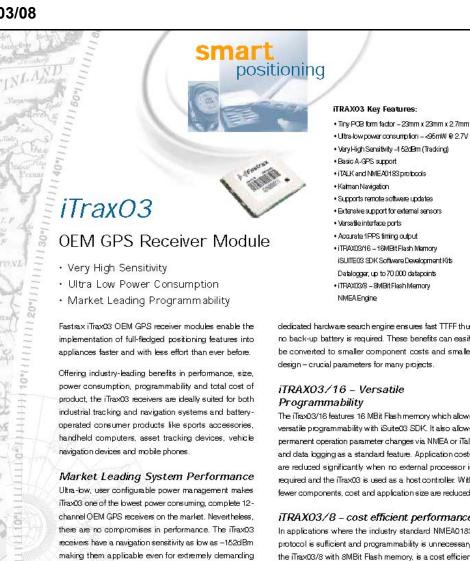

- Fastrax iTrax03/8, a 12-channel GPS receiver. iTrax03/8 features low power consumption, small footprint, 8Mbit internal Flash and does not require battery backup. For further details see Fastrax iTrax03/8, page 100.

- Motorola iO270, a wireless modem that provides packet data, circuit data and voice connectivity on the iDEN 800MHz network. The iO270 include a GPS receiver. For further details see Motorola iO270, page 102.

For further details about this modem see the section ZEUS Modem-1, page 110.

ZEUS Modem-2 supports the following wireless module with built-in GPS receiver:

Telit GE863-GPS module, which supports communication services in quad-band EGSM 850/900/1800/1900MHz networks. For further details see <u>Telit GE863-GPS</u>, page <u>104</u>.

For further details about ZEUS Modem-2, see the section ZEUS Modem-2, page 110.

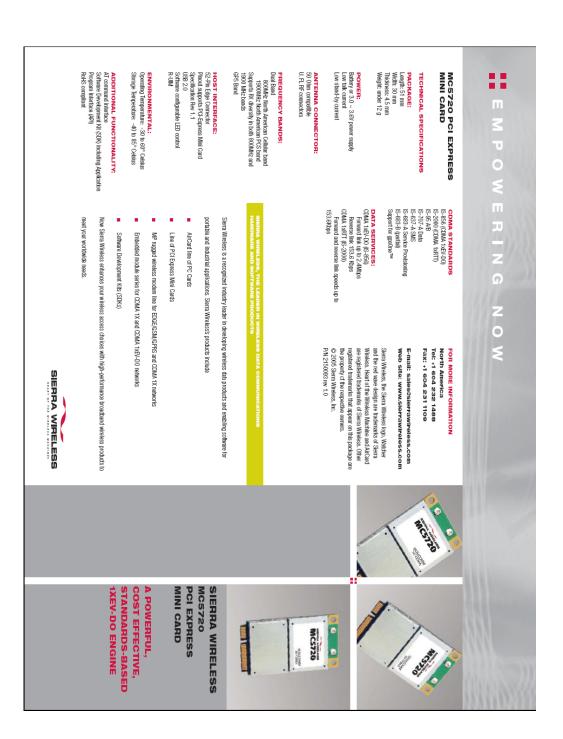

ZEUS Modem-3 supports the following wireless modules:

- Sierra Wireless MC8775 PCI Express Mini Card embedded module, which offers connectivity to all three HSDPA/UMTS frequency bands (850, 1900, 2100 MHz) and all four EDGE/GPRS bands (850, 900, 1800 and 1900 MHz) used worldwide. For further details see <u>Sierra Wireless MC8775</u>, page <u>106</u>.

- Sierra Wireless MC5720 PCI Express Mini Card embedded module, which offers a complete wireless data solution over CDMA 1x EVDO networks with typical download data rates of 400-700 kbps. For further details see <u>Sierra Wireless</u> MC5720, page 108.

- Fastrax iTrax03/16, a 12-channel GPS receiver. iTrax03/16 features low power consumption, small footprint, 16Mbit internal Flash and does not require battery backup. For further details see <u>Fastrax iTrax03/8</u>, page <u>100</u>.

For further details about ZEUS Modem-3, see the section ZEUS Modem-3, page 111.

## IEEE802.15.4 / ZigBee module (ZMx)

IEEE802.15.4 / ZigBee is the wireless standards-based technology that addresses the unique needs of remote monitoring and control for sensor level network applications. ZigBee enables deployment of wireless networks with low cost, low power solutions sensor devices and offers the ability to run remote sensors for years on inexpensive primary batteries. For more information, see <a href="https://www.zigbee.org/en/about/">www.zigbee.org/en/about/</a>.

The ZigBee module is connected to the PXA270 processor using BTUART serial interface (Rx, Tx, RTS#, CTS#). For the connector details see the section <u>J21 – IEEE802.15.4 / ZigBee connector</u>, page <u>82</u>.

Issue E (35)

# **Expansion interfaces**

There are three expansion interfaces on the ZEUS: SDIO, PC/104 and CompactFlash. PC/104 and CompactFlash interfaces are connected to the PC card memory controller of the PXA270 with the use of some 'glue logic' implemented in a CPLD (Xilinx XC9536XL). There is a CPLD Firmware version/issue register that can be accessed at the address 0x12000000.

# CPLD ver/issue register [REG0]

| Byte lane | Most significant byte Least significant byte |    |    |    |    |    |   |   |                 | ficant byte   |  |  |  |

|-----------|----------------------------------------------|----|----|----|----|----|---|---|-----------------|---------------|--|--|--|

| Bit       | 15                                           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | [7:4]           | [3:0]         |  |  |  |

| Field     | -                                            | -  | -  | -  | -  | -  | - | - | VER[3:0]        | ISSUE[3:0]    |  |  |  |

| Reset     | Х                                            | X  | Х  | Х  | Χ  | Х  | Χ | X | Current Version | Current Issue |  |  |  |

| R/W       | -                                            | -  | -  | -  | -  | -  | - | - | Read Only       |               |  |  |  |

| Address   | 0x12000000                                   |    |    |    |    |    |   |   |                 |               |  |  |  |

## **SDIO**

The SD card socket J22 is interfaced directly to PXA270's MMC/SD/SDIO controller.